Name: SQ7705 Brief Datasheet

Version: V1.0

# **SQ7705 Brief Datasheet V1.0**

Page: 1/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

# SQ7705, 16-bit Low Powr Secure MCU 64K Bytes Flash, 8K Bytes EEPROM, 8K Bytes SRAM, ADC, AES, SHA, Secure Boot

### Features

- Max. System Frequency 48 MHz

- Instruction Set is Compatible with Toshiba TLCS-870/C1

- Operating Voltage: 2.0V ~ 5.5V

- Operating Temperature: -40°C ~ 85°C

- Deep Sleep Mode Current < 1uA

### Memory Configuration

- SRAM 8K Bytes

- Flash 64K Bytes (512bytes / sector)

- EEPROM 8K Bytes (32bytes / sector)

- EEPROM and Code Flash support dual operation

### **Clock Source**

- External High Frequency Crystal : 1~16 MHz

- External Low Frequency Crystal: 32.768 KHz

- Syetem Frequency Up to 48MHz (via PLL)

- Internal Low Frequency Oscillator: 32KHz

### Timer/Counter

- Three 16-bit Timer (TCA), with timer mode, external . trigger timer mode, pulse width measurement mode, PPG mode.

- Six 8/16-bit Timer(Timer A), complementary PWM output with dead time

- Real-time Clock (RTC)

- Time Base Timer (TBT)

- Watchdog Timer (WDT)

- System Timer (STM)

- Divider Output (DVO)

### I/O

- 53 I/O for 64pin Package •

- 8 external interrupt input (EINT0~EINT7)

- 16 Key-on Wakeup (KWI0~KWI 15)

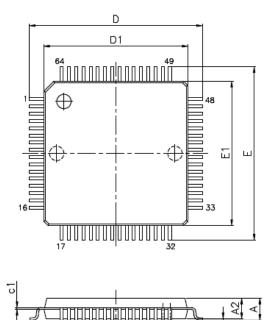

### Pacakge Type

LQFP 64 (10x10)

### 12-bit ADC

- 16 CH ADC input •

- ADC Vref

### DMA

4CH for Performance Demanding Applications

### Peripherals

- 1 set Low Energy UART

- 3 sets UART

- 2 sets I2C (max. 400KHz)

- 2 sets SPI (max. 10MHz)

### Hardware Accelerated Symmetric Crypto Engine

- SHA2-256 Hash Engine

- AES-128/AES-256 (ECB, CBC, CFB, CTR, OFB) with Side **Channel Attack Countermeasures**

- Up to 2.9Mbps hardware acceleration engine(AES) for data encryption/decryption, which is useful for realtime voice and audio encryption/decryption applications

### NIST CAVP Certified Cryptographic Algorithms

- DRBG (SP800-90A)

- TRNG (SP800-22 Compliant)

- AES-128/AES-256 (FIPS 197)

- SHA-256 (FIPS 180-4)

### Hardware-isolated, Secure Execution Environment

- Support Secure Zone and Secure Peripherals

- Support Secure Bootloader and Anti-Tamper

- Secure Memory (SRAM, Flash, EEPROM)

### Applications

- Smart Home, Smart Lock,

- **BMS** System

- Wireless Node Device

- IoT Application

Page: 2/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

|      | Technology Inc.              |                                      |               |

|------|------------------------------|--------------------------------------|---------------|

| No.: | TDDS01-S7705-EN(B)           | Name: SQ7705 Brief Datasheet         | Version: V1.0 |

|      | ntent                        |                                      | 2             |

|      |                              |                                      |               |

|      |                              |                                      |               |

|      |                              |                                      |               |

|      |                              |                                      |               |

|      |                              | ΠΟΝ                                  |               |

|      | ,                            |                                      |               |

|      |                              | RISTICS                              |               |

|      |                              | IG                                   |               |

|      |                              | ~~                                   |               |

|      | -                            | ns                                   |               |

|      |                              | s                                    |               |

|      |                              |                                      |               |

|      |                              | TERISTICS                            |               |

|      |                              |                                      |               |

| 3.0  | <b>5 LVD CHARACTERISTICS</b> |                                      | 26            |

|      |                              |                                      |               |

|      |                              |                                      |               |

|      |                              | S                                    |               |

| 4.   | ADDRESSING SPACE             |                                      | 29            |

|      |                              |                                      |               |

| 4.2  | 2 DATA MEMORY                |                                      | 31            |

| 5.   | SYSTEM OPERATION             |                                      |               |

| 5.   | OPERATING MODES              |                                      |               |

| 6.   | MEMORY PROTCTION U           | NIT (OPERATE IN ADM MODE, USER MODE) |               |

| 6.   | I FUNCTION                   |                                      |               |

| APPI | ENDIX A. PRODUCT NUN         | IBER INFORMATION                     |               |

|      |                              | RMATION                              |               |

|      |                              |                                      |               |

|      | . ,                          |                                      |               |

| KEVI |                              |                                      |               |

Page: 3/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

# 2. Product Overview

# 2.1 Features

| Product No.                       | SQ7705LA064SGGR                                                   |  |  |

|-----------------------------------|-------------------------------------------------------------------|--|--|

| Pins/ (IOs)                       | 64 / (53)                                                         |  |  |

| Operating Voltage                 | 2.0~5.5V                                                          |  |  |

| Operating Temp.                   | -40~85°C                                                          |  |  |

| External Interrupt                | 16                                                                |  |  |

| Flash                             | 64K Bytes                                                         |  |  |

| EEPROM                            | 8K Bytes                                                          |  |  |

| RAM                               | 8K Bytes                                                          |  |  |

| ADC                               | 12-bit x16-CH<br>(VDD,External)                                   |  |  |

| Interrupt                         | External : 8<br>Internal : 44                                     |  |  |

| Internal Oscillator /<br>Accuracy | 48MHz<br>+/- 1% @ 0~50℃<br>+/- 1.5% @ -20~70℃<br>+/- 3% @ -40~85℃ |  |  |

| External Crystal                  | 1~16MHz ,32768Hz                                                  |  |  |

| BROR 1 Level                      |                                                                   |  |  |

| LVD                               | 8 Levels<br>(+/- 3%) <sup>*2</sup>                                |  |  |

|                                   | 8/16-bit Timer A x 3                                              |  |  |

| Timer /<br>Counter                | 16-bit TCA x 3                                                    |  |  |

|                                   | WDT,TBT,RTC,STM                                                   |  |  |

| PWM/PPG                           | 8/16-bit Timer A x 3                                              |  |  |

|                                   | 16-bit TCA x 3                                                    |  |  |

| Communication                     | LEUART x 1 ,UART x 3<br>SPI x 2 , I2C x 2                         |  |  |

| OCDE                              | Yes                                                               |  |  |

| Package Type                      | LQFP64(10x10)                                                     |  |  |

Note 1:" VDD" means using VDD as internal reference voltage; "external" means there is on external reference voltage Note 2: Detail accuracy please refer to " 3.6 LVD characteristics

Page: 4/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.0

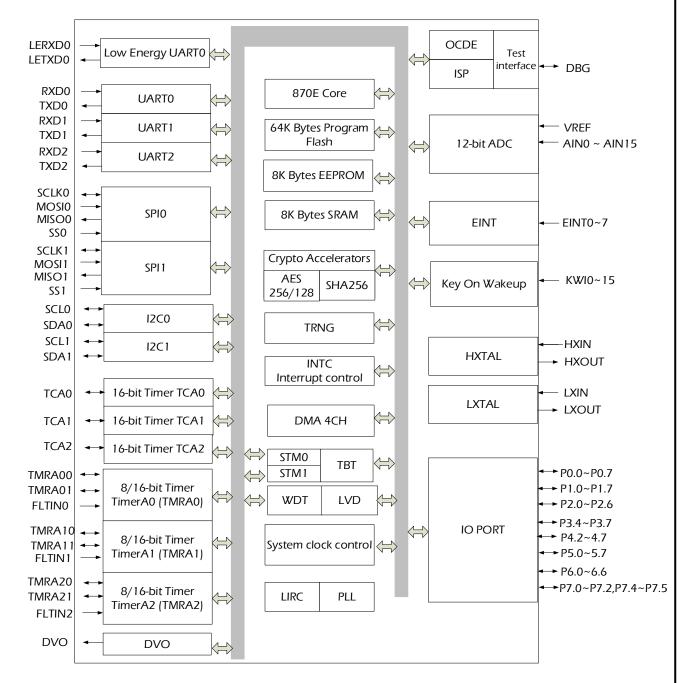

# 2.2 Block Diagram

Figure 2.1 SQ7705 Block Diagram

TimerA (TMRA) is 8/16-bit timer/counter; TMRA00 and TMRA01 are timer/counter input/output function. 1.

Page: 5/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

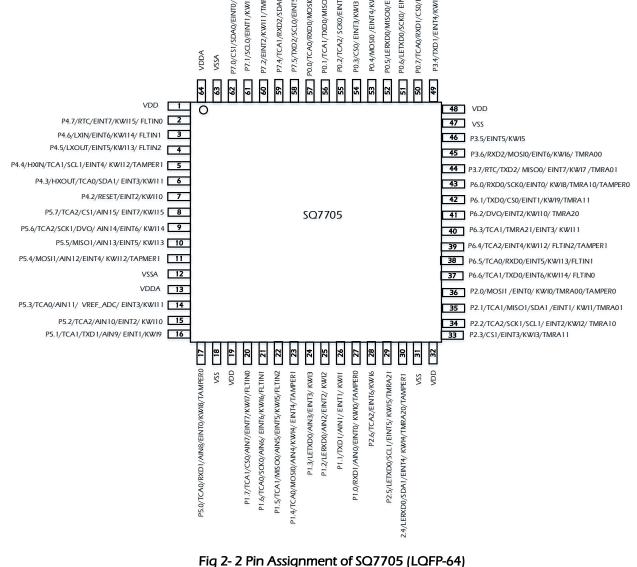

iMQ Technology Inc. No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.0 2.3 Pin Assignment/ Description Product No.: SQ7705LA064SGGR (LQFP64 10x10) P0.0/TCA0/RXD0/MOSI0/KWI0/EINT0/TMRA11/TAMPER0 P7.4/TCA1/RXD2/SDA0/ EINT4/KWI13/TMRA01 P0.1/TCA1/TXD0/MISO0/EINT1/KWI1/TMRA20 P7.5/TXD2/SCL0/EINT5/ KWI14/TMRA10 P0.2/TCA2/ SCK0/EINT2/ KWI2/TMRA2 P0.4/MOSI0 /EINT4/KWI4/TAMPER1 P0.5/LERXD0/MISO0/EINT5/KWI5/ P0.7/TCA0/RXD1/CS0/EINT7/KWI7 P0.6/LETXD0/SCK0/ EINT6 /KW16 P3.4/TXD1/EINT4/KWI4/DBG P7.0/CS1/SDA0/EINT0/KWI9 P7.2/EINT2/KWI11/TMRA00 P7.1/SCL0/EINT1/KWI10

Page: 6/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

| lo.:       | lo.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.0 |                 |                                                                                                                                                                                                                                                                                                                |  |  |

|------------|--------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 64<br>Pin. | Pin Name/Pin Option                                                | I/О Туре        | Function Description                                                                                                                                                                                                                                                                                           |  |  |

| 1          | VDD                                                                | Power           | Positive power supply.                                                                                                                                                                                                                                                                                         |  |  |

| 2          | P4.7/RTC/EINT7/KWI15/<br>FLTIN0                                    | I/O<br>(Type A) | P4.7 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>RTC, external interrupt EINT7, wake up pin KWI15, 8/16-bit timer FLTIN0 input<br>are pin-shared with P4.7.                                                                                   |  |  |

| 3          | P4.6/LXIN/EINT6/KWI14/<br>FLTIN1                                   | I/O<br>(Type B) | P4.6 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>LXIN, external interrupt EINT6, wake up pin KWI14, 8/16-bit timer FLTIN1 input<br>are pin-shared with P4.6. LXIN is connected to low frequency external crystal.                             |  |  |

| 4          | P4.5/LXOUT/EINT5/KWI13/<br>FLTIN2                                  | I/O<br>(Type B) | P4.5 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>LXOUT, external interrupt EINT5, wake up pin KWI13, 8/16-bit timer FLTIN2 inpur<br>are pin-shared with P4.5. LXOUT is connected to low frequency external<br>crystal.                        |  |  |

| 5          | P4.4/HXIN/TCA1/SCL1/EINT4<br>/ KWI12                               | I/O<br>(Type B) | P4.4 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>HXIN, 16-bit timer TCA1, SCL1(I2C bus clock input/output), external interrupt<br>EINT4, wake up pin KWI1 are pin shared with P4.4. HXIN is connect to high<br>frequency external crystal.    |  |  |

| 6          | P4.3/HXOUT/TCA0/SDA1/<br>EINT3/KWI11                               | I/О<br>(Туре В) | P4.3 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>HXOUT, 16-bit timer TCA0, SDA1 (I2C bus data input/output), external interrup<br>EINT3, wake up pin KWI11 are pin-shared with P4.3. HXOUT is connected to hig<br>frequency external crystal. |  |  |

| 7          | P4.2/RESET/EINT2/KWI10                                             | I/O<br>(Type A) | P4.2 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>External interrupt EINT2, wake up pin KWI10 are pin-shared with P4.2.<br>RESET is pin-shared with P4.2. Reset is low-active.                                                                 |  |  |

| 8          | P5.7/TCA2/CS1/AIN15/<br>EINT7/KWI15                                | I/O<br>(Type C) | P5.7 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>16-bit timer TCA2, CS1 (SPI chip select), ADC input AIN15, external interrupt EINT7<br>wake up pin KWI15 are pin-shared with P5.7.                                                           |  |  |

| 9          | P5.6/TCA2/SCK1/DVO/<br>AIN14/EINT6/ KWI14                          | I/O<br>(Type C) | P5.6 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistors.<br>16-bit timer TCA2, SCK1 (SPI clock), devider output(DVO), ADC input AIN14,<br>external interrupt EINT6, wake up pin KWI14 are pin-shared with P5.6.                                          |  |  |

Page: 7/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

| 64<br>Pin. | Pin Name/Pin Option                       | I/О Туре        | e Function Description                                                                                                                                                                                                                                                                              |  |  |  |

|------------|-------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 10         | P5.5/MISO1/AIN13/EINT5/<br>KWI13          | I/O<br>(Type C) | P5.5 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>MISO1 (SPI master in salve out), ADC input AIN13, external interupt EINT5, wake<br>up pin KWI13 are pin-shared with P5.5.                                                          |  |  |  |

| 11         | P5.4/MOSI1/AIN12/EINT4/<br>KWI12          | I/O<br>(Type C) | P5.4 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>MOSI1(SPI master out slave in), ADC input AIN12, external interrupt EINT4, wake<br>up pin KWI12 are pin-shared with P5.4.                                                          |  |  |  |

| 12         | VSSA                                      | GND             | Analog power ground                                                                                                                                                                                                                                                                                 |  |  |  |

| 13         | VDDA                                      | Power           | Analog positive power supply.                                                                                                                                                                                                                                                                       |  |  |  |

| 14         | P5.3/TCA0/AIN11/<br>VREF_ADC/ EINT3/KWI11 | I/O<br>(Type C) | P5.3 is bi-directional I/O pins, which are software configurable to be with pull-<br>or pull-down resistor.<br>16-bit timer TCA0, ADC input AIN11, VREF_ADC, external interrupt EINT3, w<br>up pin KWI11 are pin-shared with P5.3.                                                                  |  |  |  |

| 15         | P5.2/TCA2/AIN10/EINT2/<br>KWI10           | I/O<br>(Type C) | <ul> <li>P5.2 is bi-directional I/O pins, which are software configurable to be with pull-to or pull-down resistor.</li> <li>16-bit timer TCA2, ADC input AIN10, external interrupt EINT2, wake up pin KWI10 are pin-shared with P5.2.</li> </ul>                                                   |  |  |  |

| 16         | P5.1/TCA1/TXD1/AIN9/<br>EINT1/KWI9        | I/O<br>(Type C) | P5.1 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA1, UART TXD1, ADC input AIN9, external interrupt EINT1, wake<br>up pin KWI9 are pin-shared with P5.1.                                                              |  |  |  |

| 17         | P5.0/TCA0/RXD1/AIN8/EINT<br>0/KW18        | I/O<br>(Type C) | <ul> <li>P5.0 is bi-directional I/O pins, which are software configurable to be with pull-or pull-down resistor.</li> <li>16-bit timer TCA0, UART RXD1, ADC input AIN8, external interrupt EINT0, wake pin KWI8 are pin-shared with P5.0.</li> </ul>                                                |  |  |  |

| 18         | vss                                       | GND             | Ground                                                                                                                                                                                                                                                                                              |  |  |  |

| 19         | VDD                                       | Power           | Positive power supply.                                                                                                                                                                                                                                                                              |  |  |  |

| 20         | P1.7/TCA1/CS0/AIN7/EINT7/<br>KWI7/FLTIN0  | I/O<br>(Type C) | <ul> <li>P1.7 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.</li> <li>) 16-bit timer TCA1, CS0 (SPI chip select), ADC input AIN7, external interrupt EINT7 wake up pin KWI7,8/16-bit timer FLTIN0 input are pin-shared with P1.7.</li> </ul> |  |  |  |

Page: 8/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

| 64<br>Pin. | Pin Name/Pin Option                        | I/О Туре        | Function Description                                                                                                                                                                                                                                                                         |  |  |  |

|------------|--------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 21         | P1.6/TCA0/SCK0/AIN6/<br>EINT6/KWI6/FLTIN1  | I/O<br>(Type C) | P1.6 is bi-directional I/O pins, which are software configurable to be with pull-<br>or pull-down resistor.<br>16-bit timer TCA0, SCK0 (SPI clock input/output), ADC input AIN6, exter<br>interrupt EINT6, wake up pin KWI6, 8/16-bit timer FLTIN1 input are pin-shared v<br>P1.6.           |  |  |  |

| 22         | P1.5/TCA1/MISO0/AIN5/EIN<br>T5/KWI5/FLTIN2 | I/O<br>(Type C) | P1.5 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA1, MISOO (SPI master in slave out), ADC input AIN5, external<br>interrupt EINT5, wake up pin KWI5, 8/16-bit timer FLTIN2 input are pin-shared<br>with P1.5. |  |  |  |

| 23         | P1.4/TCA0/MOSI0/AIN4/KWI<br>4/ EINT4       | I/O<br>(Type D) | P1.4 is bi-directional I/O pins, which are software configurable to be with pull-u<br>or pull-down resistor.<br>16-bit timer TCA0, MOSI0(SPI master out slave in), ADC input AIN4, external<br>interrupt EINT4, wake up pin KWI4 are pin-shared with P1.4.                                   |  |  |  |

| 24         | P1.3/LETXD0/AIN3/EINT3/<br>KWI3            | l/O<br>(Type C) | P1.3 is bi-directional I/O pins, which are software configurable to be with pu<br>or pull-down resistor.                                                                                                                                                                                     |  |  |  |

| 25         | P1.2/LERXD0/AIN2/EINT2/<br>KWI2            | I/O<br>(Type C) | P1.2 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>Low energy UART LERXD0, ADC input AIN2, external interrupt EINT2, wake up<br>pin KWI2 are pin-shared with P1.2.                                                             |  |  |  |

| 26         | P1.1/TXD1/AIN1/ EINT1/<br>KWI1             | I/O<br>(Type C) | P1.1 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>UART TXD1, ADC input AIN1, external interrupt EINT1, wake up pin KWI1 are pin-<br>shared with P1.1.                                                                         |  |  |  |

| 27         | P1.0/RXD1/AIN0/EINT0/<br>KWI0              | I/O<br>(Type C) | P1.0 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>UART RXD1, ADC input AIN0, external interrupt EINT0, wake up pin KWI0 are pin-<br>shared with P1.0.                                                                         |  |  |  |

| 28         | P2.6/TCA2/EINT6/KWI6                       | I/O<br>(Type C) | P2.6 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA2, external interrupt EINT6, wake up pin KWI6 are pin-shared with<br>P2.6.                                                                                  |  |  |  |

Page: 9/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

| 64<br>Pin. | Pin Name/Pin Option                         | I/О Туре        | Function Description                                                                                                                                                                                                                                                                                |  |  |  |

|------------|---------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 29         | P2.5/LETXD0/SCL1/EINT5/<br>KWI5/TMRA21      | I/O<br>(Type C) | P2.5 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>Low energy UART LETXD0, SCL1 (I2C clock input/output), external interrupt<br>EINT5, wake up pin KWI5, 8/16-bit timer TMRA21 are pin-shared with P2.5.                              |  |  |  |

| 30         | P2.4/LERXD0/SDA1/EINT4/<br>KWI4/TMRA20      | I/O<br>(Туре С) | P2.4 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>Low energy UART LERXD0, SDA1 (I2C data input/output), external interrupt<br>EINT4, wake up pin KWI4, 8/16-bit timer TMRA20 are pin-shared with P2.4.                               |  |  |  |

| 31         | VSS                                         | GND             | Ground                                                                                                                                                                                                                                                                                              |  |  |  |

| 32         | VDD                                         | Power           | Positive power supply.                                                                                                                                                                                                                                                                              |  |  |  |

| 33         | P2.3/CS1/EINT3/KWI3/TMRA<br>11              | I/O<br>(Type A) | <ul> <li>P2.3 is bi-directional I/O pins, which are software configurable to be with pull or pull-down resistor.</li> <li>CS1(SPI chip select), external interrupt EINT3, wake up pin KWI3, 8/16-bit time TMRA11 are pin-shared with P2.3.</li> </ul>                                               |  |  |  |

| 34         | P2.2/TCA2/SCK1/SCL1/<br>EINT2/KWI2/TMRA10   | I/O<br>(Type A) | P2.2 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA2, SCK1(SPI clock input/output), SCL1( I2C clock input/output),<br>external interrupt EINT2, wake up pin KWI2, 8/16-bit timer TMRA10 are pin-<br>shared with P2.2. |  |  |  |

| 35         | P2.1/TCA1/MISO1/SDA1<br>/EINT1/ KWI1/TMRA01 | I/О<br>(Туре А) | P2.1 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA1, MISO1(SPI master in slave out), SDA1(I2C data input/output),<br>external interrupt EINT1, wake up pin KWI1, 8/16-bit timer TMRA01are pin-<br>shared with P2.1.  |  |  |  |

| 36         | P2.0/MOSI1 /EINT0/<br>KWI0/TMRA00           | I/O<br>(Type A) | <ul> <li>P2.0 is bi-directional I/O pins, which are software configurable to be with pu or pull-down resistor.</li> <li>A) MOSI1(SPI master out slave in), external interrupt EINT0, wake up pin KWI0, bit timer TMRA00 are pin-shared with P2.0.</li> </ul>                                        |  |  |  |

| 37         | P6.6/TCA1/TXD0/EINT6/KWI<br>14/ FLTIN0      | I/O<br>(Type A) | P6.6 is bi-directional I/O pins, which are software configurable to be with pull-<br>or pull-down resistor.<br>A) 16-bit timer TCA 1, UART TXD0, external interrupt EINT6, wake up pin KWI14,<br>8/16-bit timer FLTIN0 input are pin-shared with P6.6.                                              |  |  |  |

Page: 10/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

| 64<br>Pin. | Pin Name/Pin Option                         | I/О Туре        | Function Description                                                                                                                                                                                                                                     |  |  |  |

|------------|---------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 38         | P6.5/TCA0/RXD0/EINT5/KWI<br>13/FLTIN1       | I/O<br>(Type A) | P6.5 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA0, UART RXD0, external interrupt EINT5, wake up pin KWI13,<br>8/16-bit timer FLTIN1 input are pin-shared with P6.5.     |  |  |  |

| 39         | P6.4/TCA2/EINT4/KWI12/<br>FLTIN2            | I/O<br>(Type A) | P6.4 is bi-directional I/O pins, which are software configurable to be with pull-u<br>or pull-down resistor.<br>16-bit timer TCA2, external interrupt EINT4, wake up pin KWI12, 8/16-bit timer<br>FLTIN2 input are pin-shared with P6.4.                 |  |  |  |

| 40         | P6.3/TCA1/TMRA21/EINT3/<br>KWI11            | I/O<br>(Type A) | P6.3 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA1, external interrupt EINT3,wake up pin KWI11, 8/16-bit timer<br>TMRA21 are pin-shared with P6.3.                       |  |  |  |

| 41         | P6.2/DVO/EINT2/KWI10/<br>TMRA20             | I/O<br>(Type A) | P6.2 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>Divider output DVO, external interrupt EINT2, wake up pin KWI10, 8/16-bit timer<br>TMRA20 are pin-shared with P6.2.                     |  |  |  |

| 42         | P6.1/TXD0/CS0/EINT1/KWI9/<br>TMRA11         | I/O<br>(Type A) | P6.1 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>UART TXD0, CS0(SPI chip select), external interrupt EINT1, wake up pin KWI9 are<br>pin-shared with P6.1.                                |  |  |  |

| 43         | P6.0/RXD0/SCK0/EINT0/<br>KWI8/TMRA10        | I/O<br>(Type A) | P6.0 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>UART RXD0, SCK0(SPI clock input/output), external interrupt EINT0, wake up pin<br>KWI8, 8/16-bit timer TMRA10 are pin-shared with P6.0. |  |  |  |

| 44         | P3.7/RTC/TXD2/ MISO0/<br>EINT7/KWI7 /TMRA01 | I/O<br>(Type A) | P3.7 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>RTC, UART TXD2, SPI MISO0, external interrupt EINT7, wake up pin KWI 7, 8/16<br>timer TMRA01 are pin-shared with P3.7.                  |  |  |  |

| 45         | P3.6/RXD2/MOSI0/EINT6/KW<br>I6/ TMRA00      | I/O<br>(Type A) | P3.6 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>UART RXD2, SPI MOSI0, external interrupt EINT6, wake up pin KWI6, 8/16 timer<br>TMRA00 are pin-shared with P3.6.                        |  |  |  |

| 46         | P3.5/EINT5/KWI5                             | I/O<br>(Type A) | P3.5 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.                                                                                                                                            |  |  |  |

Page: 11/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

| 64<br>Pin. | Pin Name/Pin Option                        | I/О Туре        | Function Description                                                                                                                                                                                                                                                       |  |  |  |

|------------|--------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 47         | VSS                                        | GND             | Ground                                                                                                                                                                                                                                                                     |  |  |  |

| 48         | VDD                                        | Power           | Positive power supply.                                                                                                                                                                                                                                                     |  |  |  |

| 49         | P3.4/TXD1/EINT4/KWI4/DBG                   | I/O<br>(Type A) | P3.4 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>UART TXD1, external interrupt EINT4, wake up pin KWI4 are pin-shared with P3.4.                                                                           |  |  |  |

| 50         | P0.7/TCA0/RXD1/CS0/EINT7/<br>KWI7          | I/O<br>(Type A) | P0.7 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA0, UART RXD1, CS0 (SPI chip select), external interrupt EINT7, wake<br>up pin KWI7 are pin-shared with P0.7.                              |  |  |  |

| 51         | P0.6/LETXD0/SCK0/ EINT6<br>/KWI6           | I/O<br>(Type A) | P0.6 is bi-directional I/O pins, which are software configurable to be with pull-<br>or pull-down resistor.<br>Low energy UART LETXD0, SCK0(SPI clock input/output), external interrupt EII<br>wake up pin KWI6 are pin-shared with P0.6.                                  |  |  |  |

| 52         | P0.5/LERXD0/MISO0/EINT5/<br>KWI5/          | I/O<br>(Type A) | P0.5 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>Low energy UART LERXD0, MISO0( SPI master in slave out), external interrupt<br>EINT5, wake up pin KWI5 are pin-shared with P0.5.                          |  |  |  |

| 53         | P0.4/MOSI0 /EINT4/KWI4                     | I/O<br>(Type A) | P0.4 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>MOSI0(SPI master out slave in), external interrupt EINT4, wake up pin KWI4 are pin-<br>shared with P0.4.                                                  |  |  |  |

| 54         | P0.3/CS0/ EINT3/KWI3                       | I/O<br>(Type A) | P0.3 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>CSO(SPI chip select), external interrupt EINT3, wake up pin KWI3 are pin-shared<br>with P0.3.                                                             |  |  |  |

| 55         | P0.2/TCA2/ SCK0/EINT2/<br>KWI2/TMRA21      | I/O<br>(Type A) | P0.2 is bi-directional I/O pins, which are software configurable to be with pull-to or pull-down resistor.                                                                                                                                                                 |  |  |  |

| 56         | P0.1/TCA1/TXD0/MISO0/EIN<br>T1/KWI1/TMRA20 | I/O<br>(Type A) | P0.1 is bi-directional I/O pins, which are software configurable to be with pull-u<br>or pull-down resistor.<br>16-bit timer TCA1, UART TXD0, MISO0(SPI master in slave out), external interru<br>EINT1, wake up pin KWI1, 8/16-bit timer TMRA20 are pin-shared with P0.1. |  |  |  |

Page: 12/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

| 64<br>Pin. | Pin Name/Pin Option                          | I/О Туре        | Function Description                                                                                                                                                                                                                                                                      |  |  |  |

|------------|----------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 57         | P0.0/TCA0/RXD0/ MOSI0/<br>EINT0/KWI0 /TMRA11 | I/O<br>(Type A) | P0.0 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>16-bit timer TCA0, UART RXD0, MOSI0(SPI master out slave in), external interrupt<br>EINT0, wake up pin KWI0, 8/16-bit timer TMRA11 are pin-shared with P0.0.             |  |  |  |

| 58         | P7.5/TXD2/SCL0/EINT5/<br>KWI14/TMRA10        | I/O<br>(Type A) | P7.5 is bi-directional I/O pins, which are software configurable to be with pull-u<br>or pull-down resistor.<br>UART TXD2, SCL0(I2C clock input/output), external interrupt EINT5, wake up p<br>KWI14,8/16-bit timer TMRA10 are pin-shared with P7.5.                                     |  |  |  |

| 59         | P7.4/TCA1/RXD2/SDA0/<br>EINT4/KWI13/TMRA01   | I/O<br>(Type A) | <ul> <li>P7.4 is bi-directional I/O pins, which are software configurable to be with pull or pull-down resistor.</li> <li>16-bit timer TCA1, UART RXD2, SDA0(I2C data input/output), external inter EINT4, wake up pin KWI 13, 8/16-bit timer TMRA01 are pin-shared with P7.4.</li> </ul> |  |  |  |

| 60         | P7.2/EINT2/KWI11/TMRA00                      | l/O<br>(Type A) | P7.2 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>External interrupt EINT2, wake up pin KWI11,8/16-bit timer TMRA00 are pin-shared<br>with P0.1.                                                                           |  |  |  |

| 61         | P7.1/SCL0/EINT1/KWI10                        | l/O<br>(Type A) | P7.1 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>SCL0(I2C clock input/output), external interrupt EINT1,wake up pin KWI10 are pin-<br>shared with P7.1.                                                                   |  |  |  |

| 62         | P7.0/CS1/SDA0/EINT0/KWI9                     | l/O<br>(Type A) | P7.0 is bi-directional I/O pins, which are software configurable to be with pull-up<br>or pull-down resistor.<br>CS1(SPI chip select), SDA0(I2C data input/output), external interrupt EINT0, wake<br>up pin KWI9 are pin-shared with P7.0.                                               |  |  |  |

| 63         | VSSA                                         | GND             | Analog power ground                                                                                                                                                                                                                                                                       |  |  |  |

| 64         | VDDA                                         | Power           | Analog positive power supply.                                                                                                                                                                                                                                                             |  |  |  |

Page: 13/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

iMQ Technology Inc. No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.0

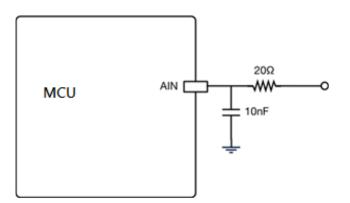

Recommended external application circuits as below figures, please follow the recommendation to design :

- 1. ADC Input Filter :

- ADC Input Filter

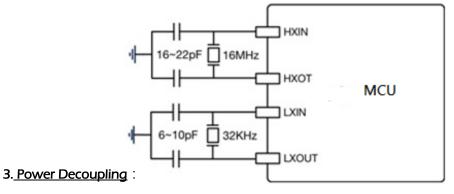

2. External Crystal :

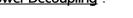

Note : The 0.1uF near the VDD should be as close as possible to the IC

Page: 14/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

| iMQ | Technology | lnc. |

|-----|------------|------|

|     |            |      |

No.: TDDS01-S7705-EN(B)

Version: V1.0

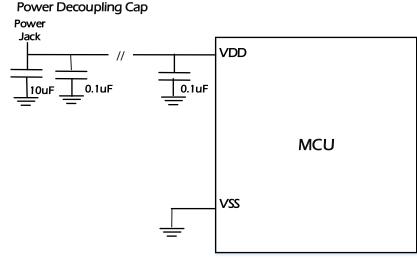

### 4. RESET and DBG pin :

Page: 15/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

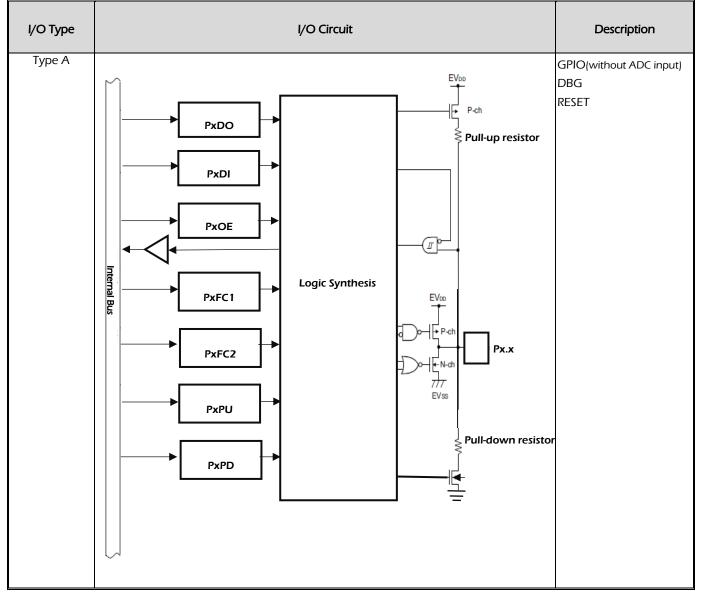

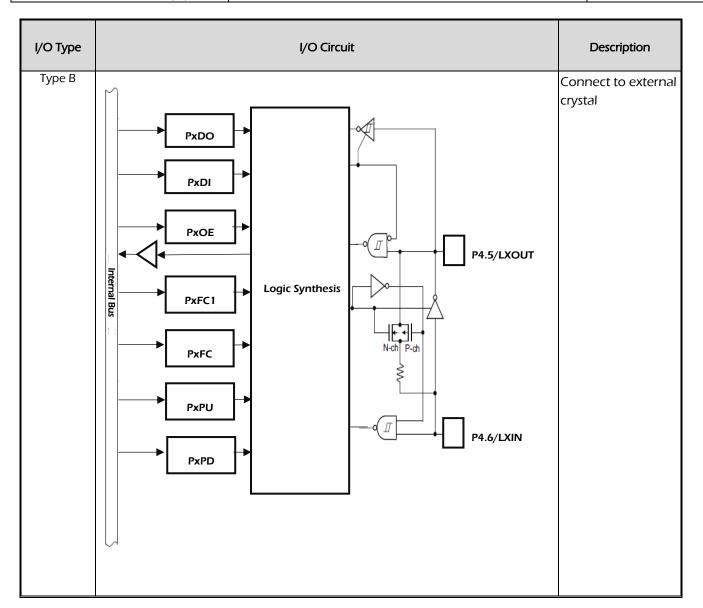

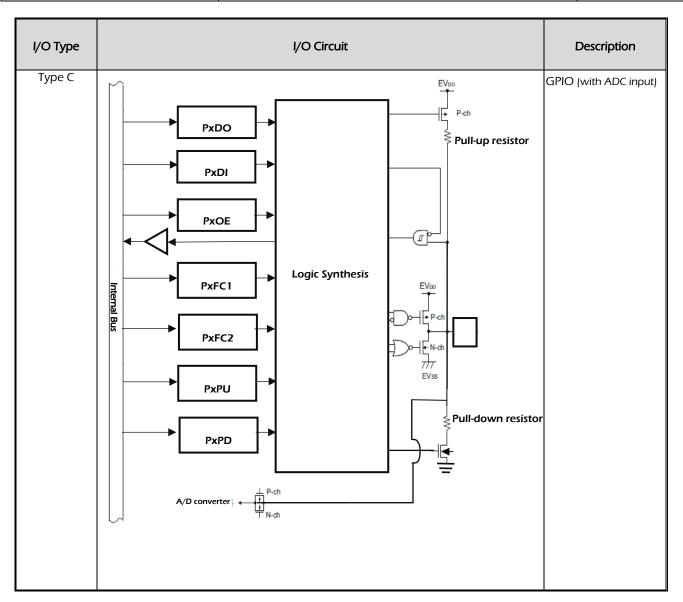

# 2.4 I/O Circuit Type

Page: 16/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

# iMQ Technology Inc.

No.: TDDS01-S7705-EN(B)

Name: SQ7705 Brief Datasheet

Version: V1.0

Page: 17/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

# iMQ Technology Inc.

No.: TDDS01-S7705-EN(B)

Name: SQ7705 Brief Datasheet

Version: V1.0

Page: 18/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

# 3. Electronic Characteristics

# 3.1 Absolute Maximum Rating

The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

|                       |                  |              | (Vs             | s = 0V |

|-----------------------|------------------|--------------|-----------------|--------|

| Parameter             | Symbol           | Pins         | Ratings         | Unit   |

| Supply Voltage        | V <sub>DD</sub>  | -            | -0.3 to 6.0     | V      |

| Input Voltage         | V <sub>IN</sub>  | All I/O pins | -0.3 to VDD+0.3 | V      |

| Output Current(total) | I <sub>OUT</sub> | All I/O pins | 100             | mA     |

| Storage Temperature   | T <sub>STG</sub> |              | -50 to 125      | °C     |

Page: 19/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

# 3.2 Operation Conditions

The following defines the electrical characteristics of the device when it is operated at voltage and temperature maximum/minimum values. Unless otherwise stated, the standard conditions were determined at "operating temperature 25 ° C and operating voltage VDD = 5 V".

# 3.2.1 Operation Conditions

| Parameter             | Symbol           | Min. | Тур. | Max. | Unit |

|-----------------------|------------------|------|------|------|------|

| Supply Voltage        | V <sub>DD</sub>  | 2.0  | 3.3  | 5.5  | V    |

| Analog Supply Voltage | V <sub>DDA</sub> | 2.0  | 3.3  | 5.5  | V    |

| Operating Temperature | Та               | -40  | 25   | 85   | °C   |

# 3.2.2 Clock Timing

| Parameter                          | Symbol            | Condition                           | Min.   | Тур.  | Max.   | Unit |

|------------------------------------|-------------------|-------------------------------------|--------|-------|--------|------|

| External Clock Source              |                   |                                     |        |       |        |      |

| Low Frequency External Crystal     | f <sub>LXIN</sub> | -                                   | _      | 32768 |        | Hz   |

| High Frequency External Crystal    | f <sub>XIN</sub>  | _                                   | 1      | _     | 16     | MHz  |

| Internal Clock Source              |                   |                                     |        | •     |        |      |

|                                    |                   | T <sub>A</sub> = 25°C               | - 1%   | 48    | + 1%   |      |

| High Frequency Internal Oscillator |                   | $T_A = 0 \sim 50^{\circ}C$ Note 2   | - 1%   | 48    | + 1%   | MHz  |

| (PLL) <sup>Note1</sup>             | f <sub>PLL</sub>  | $T_A = -20 \sim 70^{\circ}C$ Note 2 | - 1.5% | 48    | + 1.5% |      |

|                                    |                   | T <sub>A</sub> = −40~ 85°C          | - 2%   | 48    | + 2%   | 1    |

|                                    | £                 | T <sub>A</sub> = 25°C               | -15%   | 32    | + 15%  | kHz  |

| Low Frequency Internal Oscillator  | f <sub>LIRC</sub> | T <sub>A</sub> = −40~ 85°C          | -30%   | 32    | + 30%  | κπz  |

Note 1: High frequency external crystal(HXIN) can be PLL clock source. When high frequency external crystal(HXIN) is PLL clock source, the external crystal(HXIN) must be 8MHz.

Note 2: The spec is under VDD=  $5V \pm 10\%$  (4.5~5.5V) condition.

Page: 20/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

### Name: SQ7705 Brief Datasheet

Version: V1.0

# 3.2.3 I/O Characteristics

| Parameter           | Symbol              | Condition                       | Min.     | Тур. | Max.     | Unit |

|---------------------|---------------------|---------------------------------|----------|------|----------|------|

| Input low voltage   | V <sub>IL</sub>     | -                               | 0        | -    | 0.25 VDD | V    |

| Input high voltage  | VIH                 | -                               | 0.75 VDD | -    | VDD      | V    |

| V <sub>OL1</sub>    |                     | PODSEL=0,<br>IOL=5mA, VDD=5V    | -        | -    | 0.6      | V    |

| Output low voltage  | V <sub>OL2</sub>    | P0DSEL=1,<br>IOL=10mA, VDD=5V   | -        | -    | 0.6      | V    |

|                     | V <sub>OH1</sub>    | PODSEL=0,<br>IOH=1.75mA, VDD=5V | VDD-0.6  | -    | -        | V    |

| Output high voltage | V <sub>OH2</sub>    | P0DSEL=1,<br>IOH=3.5mA, VDD=5V  | VDD-0.6  | -    | -        | V    |

|                     |                     | P0DSEL=0,<br>Vo=0.1*VDD, VDD=5V | 6        | 13.5 | -        | mA   |

|                     | I <sub>OL1</sub>    | P0DSEL=0,<br>Vo=0.3*VDD, VDD=5V | 15       | 31   | -        | mA   |

| Output low current  |                     | P0DSEL=1,<br>Vo=0.1*VDD, VDD=5V | 12       | 27   | -        | mA   |

|                     | I <sub>OL2</sub>    | P0DSEL=1,<br>Vo=0.3*VDD, VDD=5V | 24       | 54   | -        | mA   |

|                     |                     | P0DSEL=0,<br>Vo=0.9*VDD, VDD=5V | 2.5      | 4.8  | -        | mA   |

| Outout high annual  | I <sub>OH1</sub>    | P0DSEL=0,<br>Vo=0.7*VDD, VDD=5V | 6.5      | 12   | -        | mA   |

| Output high current |                     | P0DSEL=1,<br>Vo=0.9*VDD, VDD=5V | 5        | 9.6  | -        | mA   |

|                     | I <sub>OH2</sub>    | P0DSEL=1,<br>Vo=0.7*VDD, VDD=5V | 13       | 24   | -        | mA   |

| Pull-up resistance  | R <sub>PULLUP</sub> | connect to pull-up resistance   | 10       | 20   | 40       | kΩ   |

| Pull-low Resistance | R <sub>PULLDN</sub> | connect to pull-down resistance | 10       | 20   | 40       | kΩ   |

Page: 21/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

### Name: SQ7705 Brief Datasheet

Version: V1.0

| Parameter           | Symb<br>ol          | Condition                         | Min.     | Тур. | Max.     | Unit |

|---------------------|---------------------|-----------------------------------|----------|------|----------|------|

| Input low voltage   | VIL                 | -                                 | 0        | -    | 0.25 VDD | V    |

| Input high voltage  | VIH                 | -                                 | 0.75 VDD | -    | VDD      | V    |

| Output low voltage  | V <sub>OL1</sub>    | P0DSEL=0,<br>IOL=2.5mA, VDD=3.3V  | -        | -    | 0.4      | V    |

| Output low voltage  | V <sub>OL2</sub>    | PODSEL=1,<br>IOL=5mA, VDD=3.3V    | -        | -    | 0.4      | V    |

|                     | V <sub>OH1</sub>    | PODSEL=0,<br>IOH=0.75mA, VDD=3.3V | VDD-0.6  | -    | -        | V    |

| Output high voltage | V <sub>OH2</sub>    | P0DSEL=1,<br>IOH=1.5mA, VDD=3.3V  | VDD-0.6  | -    | -        | V    |

|                     |                     | PODSEL=0,<br>Vo=0.1*VDD, VDD=3.3V | 2.5      | 6.7  | -        | mA   |

|                     | I <sub>OL1</sub>    | PODSEL=0,<br>Vo=0.3*VDD, VDD=3.3V | 7        | 15   | -        | mA   |

| Output low current  |                     | P0DSEL=1,<br>Vo=0.1*VDD, VDD=3.3V | 5        | 13.4 | -        | mA   |

|                     | I <sub>OL2</sub>    | P0DSEL=1,<br>Vo=0.3*VDD, VDD=3.3V | 14       | 30   | -        | mA   |

|                     |                     | P0DSEL=0,<br>Vo=0.9*VDD, VDD=3.3V | 1        | 2.4  | -        | mA   |

|                     | I <sub>OH1</sub>    | P0DSEL=0,<br>Vo=0.7*VDD, VDD=3.3V | 3        | 5.8  | -        | mA   |

| Output high current |                     | P0DSEL=1,<br>Vo=0.9*VDD, VDD=3.3V | 2        | 4.8  | -        | mA   |

|                     | I <sub>OH2</sub>    | P0DSEL=1,<br>Vo=0.7*VDD, VDD=3.3V | 6        | 11.6 | -        | mA   |

| Pull-up resistance  | R <sub>PULLUP</sub> | connect to pull-up resistance     | 10       | 20   | 40       | kΩ   |

| Pull-low Resistance | R <sub>PULLDN</sub> | connect to pull-down resistance   | 10       | 20   | 40       | kΩ   |

Page: 22/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

# 3.3 D.C. Characteristics

|                                            |                     |                                                                                                   | Operat | ing @ 3.3 | V , Ta= | -40~85°C |

|--------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------|--------|-----------|---------|----------|

| Parameter                                  | Symbol              | Condition                                                                                         | Min.   | Тур.      | Max.    | Unit     |

|                                            | I <sub>DD_N0</sub>  | System clock is PLL( clock sourcs is high<br>frequency internal oscillator)<br>fsysclk= PLL 48MHz | _      | 6.5       | _       | mA       |

| Normal Mode<br>(Code executing from Flash) | I <sub>DD_N1</sub>  | System clock is HXTAL<br>fsysclk= HXTAL16MHz                                                      | _      | 3.8       | _       | mA       |

|                                            | I <sub>DD_N2</sub>  | System clock is LIRC<br>fsysclk= LIRC 32KHz                                                       | _      | 0.7       | _       | mA       |

|                                            | I <sub>DD_N3</sub>  | System clock is LXTAL<br>fsysclk= LXTAL 32768Hz                                                   | -      | 0.7       | _       | mA       |

|                                            | I <sub>DD_SLO</sub> | System clock is PLL( clock sourcs is high<br>frequency internal oscillator)<br>fsysclk= PLL 48MHz | -      | 4.5       | _       | mA       |

| Sleep Mode                                 | I <sub>DD_SL1</sub> | System clock is HXTAL<br>fsysclk= HXTAL16MHz                                                      | Ι      | 1.3       | _       | mA       |

| (CPU clock is stopped)                     | I <sub>DD_SL2</sub> | System clock is LIRC<br>fsysclk= LIRC 32KHz                                                       | Ι      | 0.7       | _       | mA       |

|                                            | I <sub>DD_SL3</sub> | System clock is LXTAL<br>fsysclk= LXTAL 32768Hz                                                   | _      | 0.7       | _       | mA       |

| Deep Sleep Mode                            | I <sub>DD_DS0</sub> | RTC Disable                                                                                       | -      | 1.2       | _       | uA       |

| (CPU and RAM are retained)                 | I <sub>DD_DS1</sub> | RTC Enable , LXTAL On                                                                             | _      | 1.8       | _       | uA       |

| Operating @ 3.3 V , Ta= 25°C                  |                     |                       |      |      |      |      |  |  |

|-----------------------------------------------|---------------------|-----------------------|------|------|------|------|--|--|

| Parameter                                     | Symbol              | Condition             | Min. | Тур. | Max. | Unit |  |  |

| Deep Sleep Mode<br>(CPU and RAM are retained) | I <sub>DD_Dso</sub> | RTC Disable           | -    | 1.2  | -    | uA   |  |  |

|                                               | I <sub>DD_DS1</sub> | RTC Enable , LXTAL On | -    | 1.8  | -    | uA   |  |  |

Page: 23/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Version: V1.0

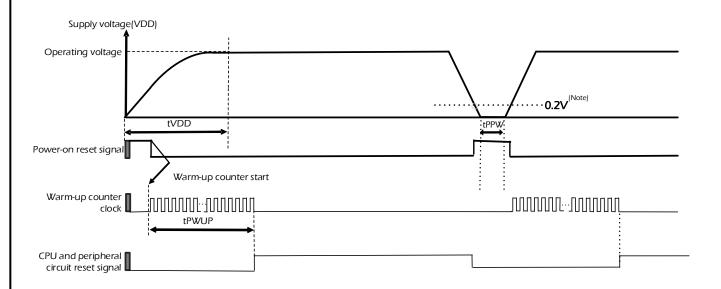

# 3.4 Power-on Reset Characteristics

|        |                                                      |      |      | Vss=0,Ta | =-40~85°C |

|--------|------------------------------------------------------|------|------|----------|-----------|

| Symbol | Condition                                            | Min. | Тур. | Max.     | Unit      |

| tPPW   | Power-on reset minimum pulse width                   | 1    | -    | -        | ms        |

| tPWUP  | Warming-up time after a reset is clear and CPU ready | -    | 4    | -        | ms        |

| tVDD   | Power supply rise time                               | 0.5  | -    | 5        | ms        |

Note: tPWUP does not include BOOTROM code execution time.

FIGURE 3-1 OPERATION TIMING OF POWER ON RESET

Note : In power-down process, the VDD must be 0V, then re-power-on to ensure the IC operating normal.

### Page: 24/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Version: V1.0

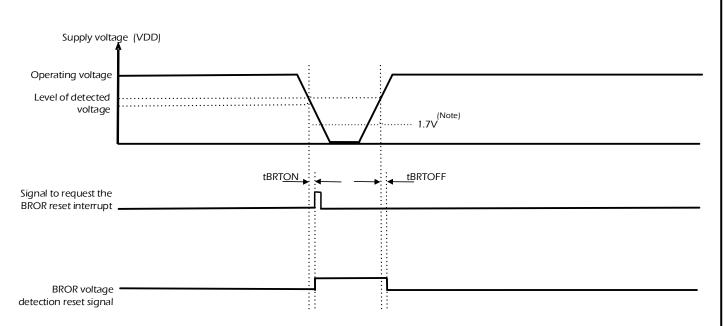

# **3.5 BROR Characteristics**

|                    |             |                                                                       |      |      |      | -40~85°C |

|--------------------|-------------|-----------------------------------------------------------------------|------|------|------|----------|

| Parameter          | Symbol      | Condition                                                             | Min. | Тур. | Max. | Unit     |

| BROR detected VBRO | OR_Rising   | VDD rise time and fall time > tVDD<br>(tVDD please refer to ch3.4 POR | 1.95 | 2.0  | 2.05 | V        |

| voltage VBR0       | OR_ Falling | characteristics )                                                     | 1.85 | 1.90 | 1.95 | V        |

### FIGURE 3-2 BROR

Note : Do not perform any operation when VDD under V1.7V. It will cause the operation abnormal.

# Page: 25/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

## Name: SQ7705 Brief Datasheet

Version: V1.0

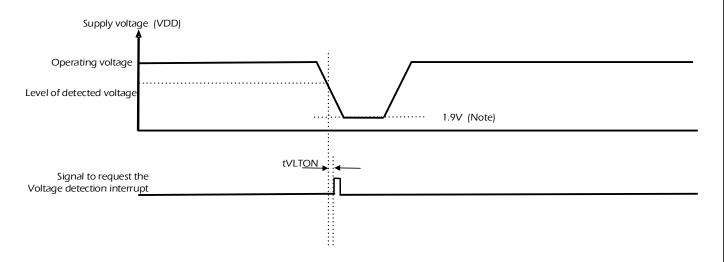

# 3.6 LVD Characteristics

|           | Ta=-40~85°C |                                                            |      |      |      |      |  |  |  |

|-----------|-------------|------------------------------------------------------------|------|------|------|------|--|--|--|

| Parameter | Symbol      | Condition                                                  | Min. | Тур. | Max. | Unit |  |  |  |

|           | VD0LVL1     | Falling Mode, LVD0CFG=000 (Note)         1.94         2.00 |      | 2.06 | V    |      |  |  |  |

|           | VD0LVL2     | Falling Mode, LVD0CFG =001                                 | 2.28 | 2.35 | 2.42 | V    |  |  |  |

|           | VD0LVL3     | Falling Mode, LVD0CFG =010                                 | 2.57 | 2.65 | 2.73 | V    |  |  |  |

| LVD       | VD0LVL4     | Falling Mode, LVD0CFG =011                                 | 2.76 | 2.85 | 2.94 | V    |  |  |  |

| LVD       | VD1LVL1     | Falling Mode, LVD1CFG=100                                  | 3.06 | 3.15 | 3.24 | V    |  |  |  |

|           | VD1LVL2     | Falling Mode, LVD1CFG=101                                  | 3.86 | 3.98 | 4.10 | V    |  |  |  |

| -         | VD1LVL3     | Falling Mode, LVD1CFG =110                                 | 4.07 | 4.20 | 4.33 | V    |  |  |  |

|           | VD1LVL4     | Falling Mode, LVD1CFG =111                                 | 4.37 | 4.50 | 4.64 | V    |  |  |  |

| Parameter | Symbol                                    | Condition | Min. | Тур. | Max. |

|-----------|-------------------------------------------|-----------|------|------|------|

| tVLTON    | Voltage detecting detection response time | -         | 1    | 10   | us   |

FIGURE 3-3 LVD

Note : It may trigger BROR.

Page: 26/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Version: V1.0

# 3.7 ADC Characteristics

|                                          |                                               |                     |                                   | VREF_/                     | ADC=VDD  |

|------------------------------------------|-----------------------------------------------|---------------------|-----------------------------------|----------------------------|----------|

|                                          |                                               |                     | 4.5V ≦                            | $VDD \leq 5.5V, T_A=$      | -40~85°C |

| Parameter                                | Symbol                                        | Min.                | Тур.                              | Max.                       | Unit     |

| Resolution                               | RESADC                                        | _                   | 12                                | _                          | bits     |

| Sampling Rate                            | f <sub>ADC</sub>                              | _                   | _                                 | 470                        | KSPS     |

| Differential Nonlinearity Error<br>(DNL) | DNL <sub>ADC</sub>                            |                     | _                                 | ±2.5                       | LSB      |

| Integral Nonlinearity Error (INL)        | INL <sub>ADC</sub>                            | _                   |                                   | ±3.5                       | LSB      |

| Gain Error                               | E <sub>GAIN</sub>                             | _                   | -                                 | ±5                         | LSB      |

| Offset Error                             | E <sub>OFFSET</sub>                           | _                   | -                                 | ±4.5                       | LSB      |

| Input Voltage Range                      | $V_{ADC_RNG}$                                 | _                   | -                                 | VDD                        | V        |

| VREF_ADC Voltage Range                   | $V_{REF\_ADC}$                                |                     | VDD <sup>Note1</sup>              |                            | V        |

| Note 1 : VERF_ADC=VDD, the v             | oltage range 4                                | .5~5.5V             |                                   |                            | •        |

| Note 2 : ADC sample rate = $\frac{1}{2}$ | $\frac{1}{2} \times \frac{fsysclk}{ADCCKDIV}$ |                     |                                   |                            |          |

| e v. When system clock is 74             | MALIZ ADCCVC                                  | NIL cot to OVOZ ADC | $Sample rate: \frac{1}{x} x^{24}$ | $^{\rm MHZ} = 272.727 kcm$ | c        |

e.x. When system clock is 24MHz, ADCCKDIV set to 0x02, ADC Sample rate :  $\frac{1}{22}x\frac{1}{2^2} = 272.727$ ksps

|                                          |                             |                       |                                            | VREF                           | _ADC=VDD    |

|------------------------------------------|-----------------------------|-----------------------|--------------------------------------------|--------------------------------|-------------|

|                                          |                             |                       | 2V ≦                                       | $VDD \leq 5.5V, T_{A}$         | ₄= -40~85°C |

| Parameter                                | Symbol                      | Min.                  | Тур.                                       | Max.                           | Unit        |

| Resolution                               | RESADC                      | -                     | 12                                         | -                              | bits        |

| Sampling Rate                            | f <sub>ADC</sub>            | _                     | -                                          | 470                            | KSPS        |

| Differential Nonlinearity Error<br>(DNL) | DNL <sub>ADC</sub>          | -                     |                                            | ±4                             | LSB         |

| Integral Nonlinearity Error (INL)        | INL <sub>ADC</sub>          | _                     | -                                          | ±5                             | LSB         |

| Gain Error                               | E <sub>GAIN</sub>           | _                     | -                                          | ±6                             | LSB         |

| Offset Error                             | E <sub>OFFSET</sub>         | _                     | -                                          | ±6                             | LSB         |

| Input Voltage Range                      | $V_{ADC_RNG}$               | _                     | -                                          | VDD                            | V           |

| VREF_ADC Voltage Range                   | $V_{REF\_ADC}$              |                       | VDD Note 1                                 |                                | V           |

| Note 1 : VERF_ADC=VDD, the v             | oltage range 2 <sup>,</sup> | ~5.5V                 |                                            |                                |             |

| Note 2 : ADC sample rate = $\frac{1}{2}$ |                             |                       |                                            |                                |             |

| e.x. When system clock is 24             | MHz, ADCCKD                 | IV set to 0x02, ADC S | Cample rate : $\frac{1}{22}x\frac{24N}{2}$ | $\frac{1}{2}^{1} = 272.727 ks$ | ps          |

Page: 27/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Version: V1.0

# 3.8 Flash Characteristics

|                                                | (032,00                                | , 2.0 V = |      |         |       |  |

|------------------------------------------------|----------------------------------------|-----------|------|---------|-------|--|

| Parameter                                      | Condition                              | Min.      | Тур. | Max.    | Unit  |  |

| Number of guaranteed writes to flash<br>memory |                                        | -         |      | 100,000 | times |  |

| Flash memory write time                        | Write Time (per byte)                  |           |      | 40      | μs    |  |

|                                                | Chip Erase                             | -         |      | 40      |       |  |

| Flash memory erase time                        | Sector Erase<br>(1 sector = 512 bytes) | _         |      | 5       | ms    |  |

### $(V_{SS} = 0V. 2.0V \le V_{DD} \le 5.5V. T_{OPR} = -40 \text{ to } 85^{\circ}\text{C})$

# 3.9 EEPROM Characteristics

### Unit Parameter Condition Min. Тур. Max. Number of guaranteed writes to 100,000 times \_\_\_ \_\_\_ EEPROM EEPROM write time Write Time (per byte) 40 μs \_\_\_ \_\_\_ Chip Erase 40 \_\_\_ \_\_\_ **EEPROM** erase time ms Sector Erase 5 \_\_\_ ---(1 sector =32 bytes)

### $(V_{SS} = 0V, 2.0V \le V_{DD} \le 5.5V, T_{OPR} = -40 \text{ to } 85^{\circ}\text{C})$

Page: 28/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

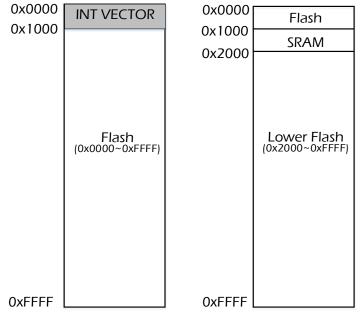

# 4. Addressing Space

The address space is divided into program and data spaces. The code and data access can be byte access or word access. The addressable memory space is 64KB of program and 64KB of data memory. This device offers MPU (Memory Protection Unit) feature. The space is able to be divided into ADM Mode and User Mode. Under ADM Mode, the user can access whole area. Under User Mode, the user can only access the area define by the setting value of MPU(Memory Protection Unit) register.

# 4.1 Program Memory

PMCFG=0x00 PMCFG=0x05 Program Memory Mapping (ADM Mode)

FIGURE 4- 1 PROGRAM MEMORY MAPPING (ADM Mode)

Page: 29/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

### iMQ Technology Inc. No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.0

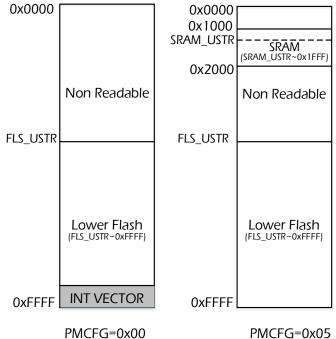

PMCFG=0x05 Program Memory Mapping (USER Mode)

FIGURE 4-2 PROGRAM MEMORY MAPPING (User Mode)

Page: 30/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

Name: SQ7705 Brief Datasheet

Version: V1.0

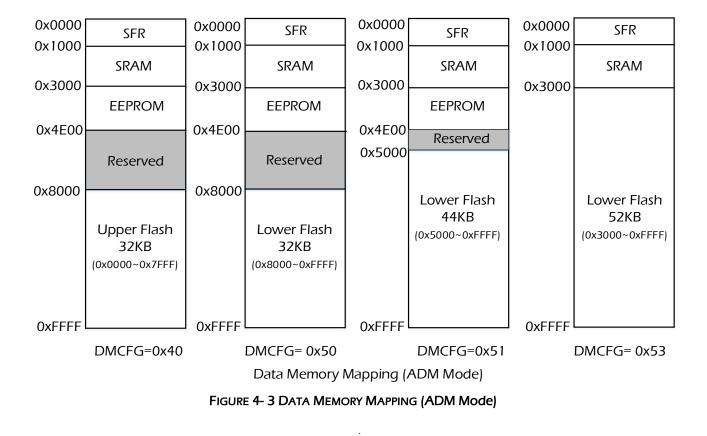

# 4.2 Data Memory

Page: 31/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

### iMQ Technology Inc. No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.0 0x0000 0x0000 SFR SFR 0x1000 0x1000 SRAM\_USTR SRAM\_USTR **SRAM** <u>S</u>RĀM (SRAM\_USTR~0x2FFF) (SRAM\_USTR~0x2FFF) 0x3000 0x3000 EEP\_USTR EEP\_USTR **EEPROM** EEPROM (EEP\_USTR~0x4DFF) (EEP\_USTR~0x4DFF) 0x4E00 0x4E00 Reserved Reserved 0x8000 0x8000 FLS\_USTR<sup>\*</sup> Lower Flash

32KB

(0x8000~0xFFFF)

DMCFG= 0x50

FIGURE 4- 4 DATA MEMORY MAPPING (User Mode)

**OxFFFF**

Data Memory Mapping (User Mode)

**Upper Flash**

32KB

(0x0000~0x7FFF)

DMCFG=0x40

**0xFFFF**

Note : FLS\_USTRcan be configured to Upper Flash orLower Flash

| Memory       | Starting address | End address |

|--------------|------------------|-------------|

| SFR          | 0x0000           | 0x0FFF      |

| SRAM         | 0x1000           | 0x2FFF      |

| EEPROM Array | 0x3000           | 0x4DFF      |

**TABLE 4-1 PERIPHERAL MEMORY MAP**

Page: 32/37 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

# 5. System Operation

# 5.1 Operating Modes

This device offers three operating modes: Normal mode, Sleep mode, and Deep sleep mode.

Normal mode is the normal operating condition. Enter either Sleep mode or Deep sleep mode, it can reduce the power dissipation. The power consumption under deep sleep mode is around 1uA.

This table summarizes the functions that are enabled/ disable under different operating modes.